Webinar: High-Speed Success at 28-56-112 Gbps with Connector-PCB Integration

REGISTER NOW

February 4th, 2026 | 9:00 AM PT

COST: FREE

-

8

Days

-

2

Hours

-

15

Minutes

-

23

Seconds

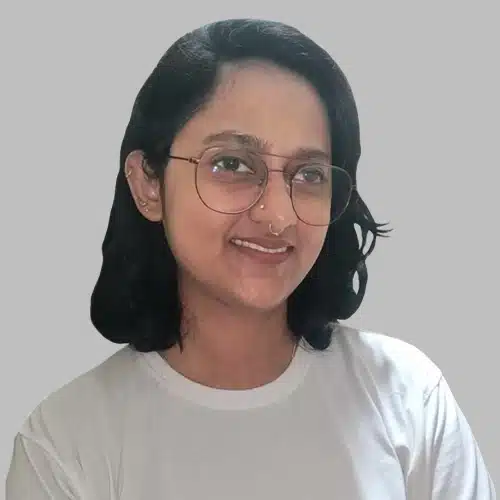

Vandana CC

Engineering Project Coordinator at Sierra Circuits

Matthew Burns

Global Director of Technical Marketing at Samtec

This webinar will be hosted on Zoom.

Following this event, you will receive:

-

Slides

-

Recording

-

Design guides

Webinar abstract:

As data rates move beyond 28 Gbps and scale rapidly to 56 and 112 Gbps, the margin for PCB design error shrinks dramatically. At these speeds, connector-PCB integration, stack-up decisions, and via design are no longer secondary considerations; they directly determine transmission line insertion loss, return loss, and overall signal integrity.

In this webinar, you’ll learn the practical techniques for high-speed PCB design with connectors. It will help you meet signal integrity targets and avoid expensive production issues.

Designing high-frequency boards with connectors

As signal speed increases, material selection becomes critical for managing insertion loss in high-speed PCB design at 28-56-112 Gbps. You should pick materials with a dissipation factor ≤0.005. Additionally, glass weave effects might introduce a skew of 1-3 ps/inch. To mitigate this, you should use spread-glass materials, such as Isola I-Speed, Tachyon-100G, and Panasonic Megtron 6.

While designing high-speed stack-ups, you must strike a balance between electrical performance and fabrication limitations. You should maintain symmetrical stack-up and avoid excessive copper weight transitions. For most high-frequency designs, ½ oz copper on signal layers offers the best balance between loss control and manufacturability.

REGISTER NOW

Controlled impedance forms the foundation of signal integrity at 28-112 Gbps. You must tightly control trace geometry, dielectric thickness, and copper roughness to keep impedance variation within acceptable limits. Target ±5% impedance tolerance and adjust trace widths for consistent impedance.

Vias often dominate high-frequency loss and reflections. Even a 10-15 mil via stub can create resonances in the 20-30 GHz range, directly impacting 56 and 112 Gbps signals. You should minimize via counts wherever possible and avoid residual stubs for critical nets.

Every high-speed signal requires a continuous return path. Any plane split or reference change might introduce impedance discontinuities and EMI. You should maintain solid reference planes under all high-speed traces. This keeps return current loops tight and reduces mode conversion, especially near connectors.

At 28-56-112 Gbps, high-speed PCB design leaves no room for guesswork. Stack-up architecture, dielectric selection, and via-in-pad geometry directly impact channel behavior, where even a few mils of dielectric variation or a single unremoved via stub might be the reason behind a failed link.

In this webinar, our experts will explain the proven methods for high-speed PCB design with connectors.

Register now to secure your spot!

Webinar agenda:

- Stack-up design for 28-112 Gbps

- o Design and layout strategies to ensure uniform impedance

- o Dielectric choices to manage glass weave effects and loss

- o Techniques for maintaining reference plane continuity

- o Common stack-up mistakes we see

- o How to design stack-ups that are manufacturable

- o Stack-up examples

- Via design that doesn’t kill your channel

- o Via stubs and aspect ratio tradeoffs

- o Via-in-pad considerations for high-speed signals

- High-speed connector breakout region (BOR) design

- o Optimized signal launch from high-speed mezzanine connectors

- o Proper via design and placement optimized SI

- o Grounding techniques to minimize discontinuities

- o BOR design evolution from 28 Gbps > 56 Gbps > 112 Gbps

About Vandana CC

With a strong foundation in physics, Vandana CC brings a deep technical understanding to her work in PCB design and electronics manufacturing. She holds a Master’s in Physics and has experience teaching before transitioning into research at the Indian Institute of Science.

At Sierra Circuits, Vandana has played a key role in R&D projects, contributing to the development of engineering tools and calculators, technical content creation, and customer demos. Currently, she focuses on project coordination, ensuring seamless collaboration both within the team and with external partners. Her expertise bridges the gap between technical innovation and practical application, making her an integral part of Sierra Circuits’ engineering efforts.

About Matthew Burns

Matthew Burns develops go-to-market strategies for Samtec’s Silicon-to-Silicon solutions. Over the course of 25+ years, he has been a leader in design, applications engineering, technical sales and marketing in the telecommunications, medical and electronic components industries. He currently serves as Secretary at PICMG. Mr. Burns holds a B.S. in Electrical Engineering from Penn State University.